Officia Fabricationis Electronicae Omnino Stabilimenta, te adiuvant ut facile producta tua electronica ex PCB et PCBA consequaris.

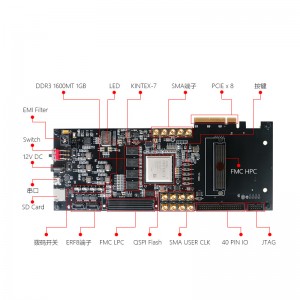

FPGA Xilinx K7 Kintex7 PCIe fibra optica communicatio

- DDR3 SDRAM: 16GB DDR3 64bit bus, celeritas datorum 1600Mbps

- Memoria QSPI Flash: Pars memoriae QSPIFLASH 128mbit, quae ad fasciculos configurationis FPGA et conservationem datorum usorum adhiberi potest.

- Interfacies PCLEX8: Interfacies PCLEX8 ordinaria ad communicationem cum PCIE tabulae matris computatralis adhibetur. Normam PCI Express 2.0 sustinet. Velocitas communicationis unius canalis usque ad 5Gbps pervenire potest.

- Portus serialis USB UART: Portus serialis, per funem miniUSB ad computatrum coniungendus ad communicationem serialem peragendam.

- Charta Micro SD: Charta Microsd sedem omnino habet, chartam Microsd ordinariam coniungere potes

- Sensor temperaturae: microplagula sensoris temperaturae LM75, quae temperaturam ambientis circa tabulam evolutionis monitorare potest.

- Portus extensionis FMC: FMC HPC et FMCLPC, quae cum variis chartis expansionis ordinariis compatibiles esse possunt.

- Terminalis connexionis celerrimae ERF8: duo portus ERF8, qui transmissionem signorum celerrimae sustinent. Extensio 40pin: interfacies extensionis generalis IO cum 2.54mm40pin reservata, O effectivum 17 paria habet, 3.3V sustinet.

- Nexus periphericus plani et plani 5V peripherica peripherica diversarum interfacierum 1O generalis usus coniungere potest.

- Terminale SMA; tredecim capita SMA aurata altae qualitatis, quae usoribus commoda sunt ut cum chartis expansionis AD/DA FMC celeritatis altae ad collectionem et processum signorum cooperentur.

- Administratio Horologii: Fons multi-horologii. Haec includunt fontem horologii differentialis systematis 200MHz SIT9102.

- Crystallus differentialis oscillans: crystallus 50MHz et microplagula administrationis horologii programmabilis SI5338P: etiam instructus cum

- Frequentiae horologii 66MHz (EMCCLK). Ad usum horologii frequentiam accurate accommodari potest.

- Portus JTAG: 10 suturae, portus JTAG 2.54mm ordinarius, ad programmata FPGA dempta et corrigenda.

- Microprocessus monitorius tensionis sub-reset: pars microprocessus monitorius tensionis ADM706R, et puga cum puga signum repositionis globale systemati praebet.

- LED: 11 lumina LED, indicant fontem potentiae tabulae, signum config_done, FMC

- Signum indicatoris potentiae, et quattuor lumina LED usoris

- Clavis et commutator: claves sex et commutatores quattuor sunt bullae reset FPGA,

- Clavis programmatis B et quattuor claves usoris componuntur. Quattuor commutatores dupliciter iaculantes cultri singularis.

Nuntium tuum hic scribe et nobis mitte.

Categoriae productorum

-

Telephonum

-

Epistula electronica

-

Whatsapp

-

Skype

-

Skype

-

Skype