Producta

-

Nova scheda matris industrialis Atom D525, potentia DC12V, scheda matris industrialis, scheda matris ITX cum scheda matris PCI, Linux.

Pars microprocessoris: Intel NM10 celeris pars microprocessoris

Processorius: Processorius Intel Atom D525 1.8G in tabula

Frequentia bus anterioris: Intel NM10 celeris chipset

Memoria Systematis: 1*SODDRIII spatium

(Memoria 800/1066, usque ad 4GB, sustinetur)

BIOS: AMI 8MB DPI Flash ROM

Functio audio: ALC662 in tabula (audio altae fidelitatis sex canalium, subsidium exitus lineae microphoni)

Extensio bus: 1 PCI

Portus monstrationis: portus VGA, et portus exitus VGA extensus

Dimensiones (L x A): 170mm x 170mm

SATA: Duae SATA 3GB/S sustinentes

Portus serialis: Duo portus COM, modus COM1/2:RS-232

Os parallelum: 1 caput putei

Portus USB: 8 portus USB 2.0 (4 in laminis posterioribus, 4 paxillis in tabula)

Interfacies PS/2: Interfacies claviaturae et muris PS/2 (tabula continet clavos ordinis claviaturae et muris 6PIN)

Portus retiarius: Una scheda retiaria RTL8105E 10/100M, initium RPL vel PXE sine disco sustinet, expergefactionem retiariam sustinet

Ostentus: GMA 3150 (Graphica Integrata CPU)

Scheda soni: Scheda soni ALC662 HD, egressus lineae, microphonum

Praebet clavum audio frontalem

Typus fontis potentiae: DC-12V

-

Rubus idaeus Pi venditor | Rubus idaeus Pi industrialis

Raspberry Pi est computatrum minutum magnitudinis chartae creditae, a Fundatione Raspberry Pi in Regno Unito designatum et elaboratum ad educationem scientiae computatralis promovendam, praesertim in scholis, ut discipuli programmandi et scientiam computatralem per praxim directam discere possint. Quamquam initio instrumentum educationale collocatum est, Raspberry PI celeriter studiosos computatrales, fabricatores, studiosos "fac-ipse" et innovatores toto orbe terrarum propter magnum gradum flexibilitatis, pretium vile et potentem copiam functionum vicit.

-

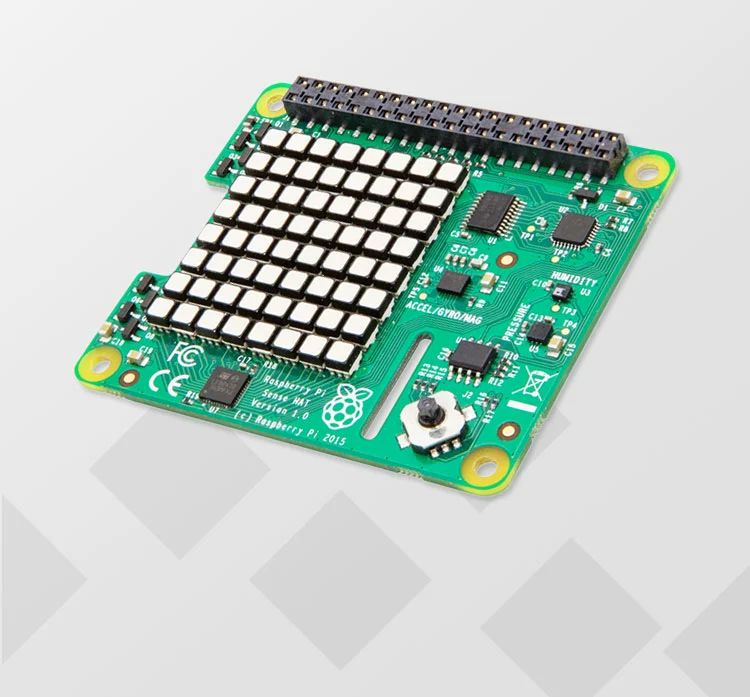

Rubus PI Sense HAT

Distributor officialis auctorizatus Raspberry Pi, fide tua dignus!

Haec est tabula expansionis sensoriae originalis Raspberry Pi quae gyroscopia, accelerometra, magnetometra, barometra, et sensoria temperaturae et humiditatis, necnon peripherica interna, ut matricem LED RGB 8×8 et oscillatorium 5-viarum, integrare potest.

-

Rubus idaeus Pi Zero W

Raspberry Pi Zero W est nova dilectissima familiae Raspberry PI, et eundem processorem ARM11-core BCM2835 utitur quo antecessor suus, circiter 40% velocius quam antea currens. Comparata cum Raspberry Pi Zero, eadem WIFI et Bluetooth quam 3B addit, quae ad plura spatia aptari possunt.

-

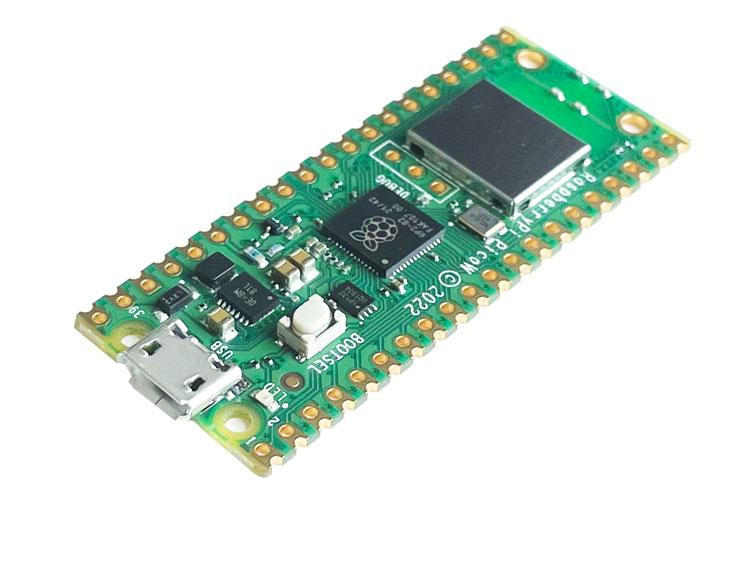

Series Pico Rubi Idaei Pi

Haec est prima tabula evolutionis microcontrollorum, in fragmento a Raspberry Pi ipso evoluto condita, quae fragmentum wireless Infineon CYW43439 addit. CYW43439 IEEE 802.11b /g/n sustinet.

Functio acus configurationis sustinetur, progressionem et integrationem flexibilem usorum facilitare potest.

Multa opera simul agere nullum tempus requirit, et imaginum conservatio celerior et facilior est.

-

Rubus idaeus Pi Zero 2W

In priore serie Zero fundata, Raspberry Pi Zero 2W notionem designandi seriei Zero adhaeret, microplaculam BCM2710A1 et 512MB memoriae RAM in tabula minima integrans, et omnes partes ingeniose in una parte collocans, quo fit ut tantam efficaciam in parvo involucro consequatur. Praeterea, etiam in dissipatione caloris singularis est, crasso strato interno cupreo utens ad calorem a processore conducendum, sine cura de problematibus altae temperaturae ex alta efficacia ortis.

-

Rubus pyricola POE+ HAT

Antequam PoE+ HAT instituas, palos cupreos provisos in quattuor angulis tabulae circuiti colloca. Postquam PoE+HAT cum portibus PoE 40-pin et 4-pin Raspberry PI coniunxisti, PoE+HAT cum instrumento PoE per funem retiaculum ad potentiam acquirendam et retiaculandum coniungi potest. Cum PoE+HAT removes, POE+HAT aequaliter trahe ut modulus leniter a palo Raspberry PI liberetur et palum flectere vites.

-

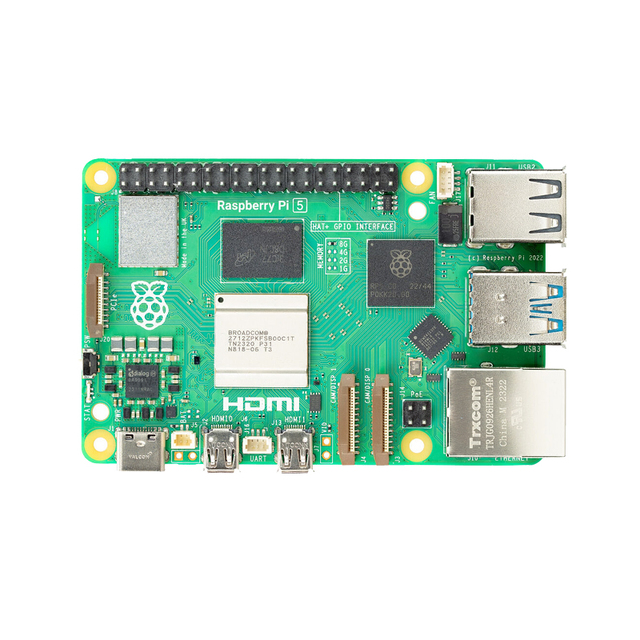

Rubus idaeus Pi 5

Raspberry Pi 5 processore Arm Cortex-A76 quadricore 64-bit, frequentia 2.4GHz operante, potentia utitur, qui efficientiam CPU bis vel ter meliorem quam Raspberry Pi 4 praebet. Praeterea, efficientia graphica GPU Video Core VII 800MHz significanter emendata est; egressus dualis ostentationis 4Kp60 per HDMI praebetur; praeter subsidium camerae provectum a processore signi imaginum Raspberry PI redesignato, usoribus experientiam escritorio lenem praebet et ianuam ad novas applicationes pro clientibus industrialibus aperit.

CPU Arm Cortex-A76 quadrinucleus 2.4GHz, 64-bit cum cella memoriae L2 512KB et cella memoriae L3 communi 2MB

GPU Video Core VII, sustinet Open GL ES 3.1, Vulkan 1.2

Duplex exitus monitorii HDMI 4Kp60 cum auxilio HDR

Decodificator 4Kp60 HEVC

LPDDR4X-4267 SDRAM (.Disponibile cum 4GB et 8GB RAM in initio)

Wi-Fi 802.11ac bifasciae⑧

Bluetooth 5.0 / Bluetooth Energiae Humilis (BLE)

Spatium pro scheda MicroSD, modum SDR104 celerem sustinens

Duo portus USB 3.0, operationem synchronam 5Gbps sustinentes

Duo portus USB 2.0

Gigabit Ethernet, subsidium PoE+ (separatum PoE+ HAT requiritur)

Duo transceptores camerae/monitoris MIPI quattuor canalium

Interfacies PCIe 2.0 x1 pro periphericis celeribus (separatum M.2 HAT vel alius adaptor requiritur)

Fons potentiae 5V/5A DC, interfacies USB-C, subsidium fontis potentiae

Acus 40 normae Rubi PI

Horologium temporis realis (RTC), a batteria externa potentiatum

Bulla potentiae

-

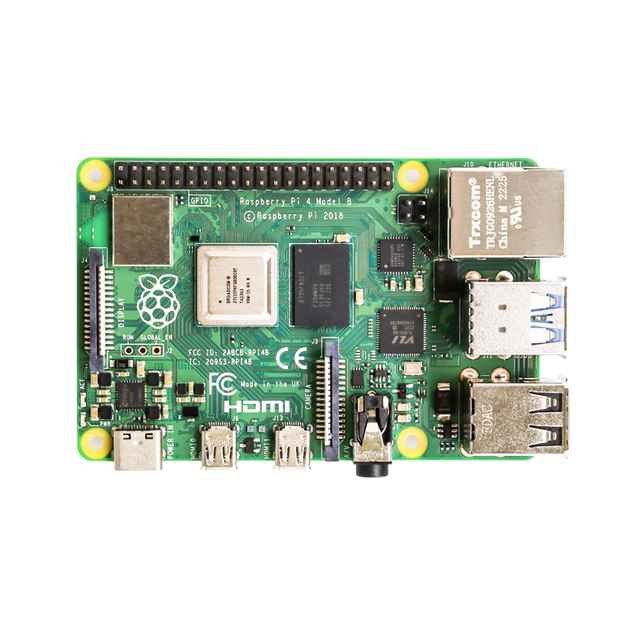

Rubus idaeus Pi 4B

Raspberry Pi 4B nova additio est familiae computatrorum Raspberry PI. Celeritas processoris significanter aucta est comparata cum priore generatione Raspberry Pi 3B+. Plurima multimedia, memoria copiosa et meliorem connectivitatem habet. Pro usoribus finalibus, Raspberry Pi 4B praebet facultatem computatri desktop comparabilem cum systematibus x86PC initialibus.

Raspberry Pi 4B habet processorem quadrum nucleorum 64-bit frequentia 1.5Ghz operantem; ostentationem duplicem cum resolutione 4K usque ad 60fps refectione; tribus optionibus memoriae praesto est: 2GB/4GB/8GB; WiFi sine filo dualis-fascia 2.4/5.0 Ghz et Bluetooth 5.0 BLE energiae humilis inclusum; unum portum Ethernet gigabit; duos portus USB 3.0; duos portus USB 2.0; unum portum potentiae 5V3A.

-

Moderator volatus Traverser Racing F7, 5V 9V, duplex BEC, OSD inclusum, F722.

Categoria Producti: Accessiones electronicae ludicrae

Origo: Shenzhen, Guangdong

Categoria ludibrii: ludicrum electricum

-

Traverser F4/F7 gubernatio volatus Beidou GPS M8N parvae magnitudinis situs celeris nexus stabilis cingulum compassus

Sensibilitas: Positio celeris nexus stabilis

Applicatio: Machina per tempus iter faciendi

Forma datorum: M8N

Series productorum: GPS

-

Machina ad dentiscalpia facienda F411+20A+35A tabula integrata gubernationis electricae volatus 2-5S AIO

Categoria Producti: Accessiones electronicae ludicrae

Categoria ludibrii: ludicrum electricum

-

Telephonum

-

Epistula electronica

-

Whatsapp

-

Skype

-

Skype

-

Skype