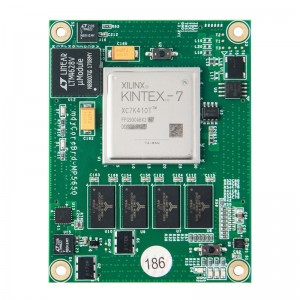

FPGA XILINX-K7 KINTEX7 XC7K325 410T Gradus Industrialis

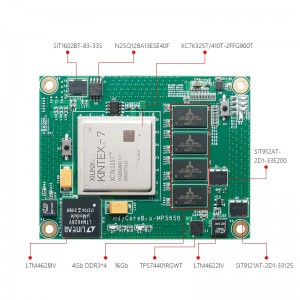

DDR3 SDRAMQ: 16GB DDR3, 4GB per unum, 16-bit Data Bit Data Bid SPI Flash: Una pars 128MBITQSPIFLASH, quae ad fasciculos configurationis FPGA et conservationem datorum usoris adhiberi potest. Gradus interfaciei FPGA Bank: adaptabiles 1.8V, 2.5V, 3.3V electrici. Si gradum mutare necesse est, tantum locum correspondentem globuli magnetici mutare debes ad adaptationem efficiendam. Fons potentiae tabulae centralis: EEPROM fons potentiae 5V-12V; M24C02-WMN6TP in instrumento bus I2C fundatur. Modum incipiendi tabulae centralis protocolli secundae lineae sequitur: duos modos incipiendi sustinet, qui sunt connectores JTAG et QSPI Flash. Portus extensus, 120-clavorum, Panasonic AXK5A2137yg MP5700, interfacies SFP laminae inferioris: 2 moduli optici communicationem fibrae opticae celerem, usque ad 6GB/s, consequi possunt. Horologium laminae inferioris: 1 horologium referentiale 200MHz cum tabula principali coniunctum. Pes tubi horologii MRCC, 1 125MHz. Lamina inferior pedum tubi horologii GTX cum tabula principali coniuncta est portus expansionis 40-clavorum: portus extensionis 40-clavorum cum spatio normali 2.54mm reservatur, qui ad modulum designatum ipsius emptoris connectendum adhibetur. Horologium tabulae centralis Essentiae: plures fontes horologii in tabula sunt. Hae includunt horologium systematis 200MHz, horologium GTX 125MHz, et horologium EMCCLK 66MHz. Portus JTAG: 10 suturae, portus JTAG ordinarius 2.54mm, ad inscriptiones LED programmatum FPGA deponendas et corrigendas: 6 lumina LED rubra in tabula principali, quae fontem potentiae tabulae indicant, 4 lumina indicantia signum et pedes tubi FPGA IO directe connexi. Claves: 4 claves. 4 claves. Hae sunt claves repositionis FPGA, claves Program_b et duae claves usoris.

FPGA Xilinx-K7 Kintex7 XC7K325 410T est exemplar specificum FPGA (Field-Programmable Gate Array) a Xilinx elaboratum. Hic sunt nonnullae res praecipuae de hac FPGA: Series: Kintex-7: FPGA seriei Kintex-7 Xilinx ad applicationes magnae efficaciae designatae sunt et bonum aequilibrium inter efficaciam, potentiam et pretium offerunt. Instrumentum: XC7K325: Hoc ad instrumentum specificum intra seriem Kintex-7 refertur. XC7K325 est una ex variantibus in hac serie praesto, et certas specificationes offert, inter quas capacitatem cellularum logicarum, segmenta DSP, et numerum I/O. Capacitas Logica: XC7K325 capacitatem cellularum logicarum 325,000 habet. Cellulae logicae sunt partes aedificatoriae programmabiles in FPGA quae configurari possunt ad circuitus et functiones digitales implementandas. Sectiones DSP: Sectiones DSP sunt opes hardware dedicatae intra FPGA quae ad officia processus signorum digitalium optimizatae sunt. Numerus exactus segmentorum DSP in XC7K325 variari potest secundum varietatem specificam. Numerus I/O: "410T" in numero exemplaris indicat XC7K325 habere in summa 410 clavos I/O usoris. Hi clavi adhiberi possunt ad interfaciem cum machinis externis vel aliis circuitibus digitalibus. Aliae Proprietates: FPGA XC7K325 alias proprietates habere potest, ut bloccos memoriae integratos (BRAM), transceptores altae celeritatis ad communicationem datorum, et varias optiones configurationis. Interest notare FPGAs sicut Xilinx-K7 Kintex7 XC7K325 esse machinas programmabiles quae tibi permittunt circuitus digitales et functiones proprias implementare programmando cellulas logicas suas. Haec flexibilitas eas aptas reddit ad amplam varietatem applicationum, inter quas computatio altae perfunctionis, processus signorum digitalium, et acceleratio ferramentorum.

Categoriae productorum

-

Telephonum

-

Epistula electronica

-

Whatsapp

-

Skype

-

Skype

-

Skype