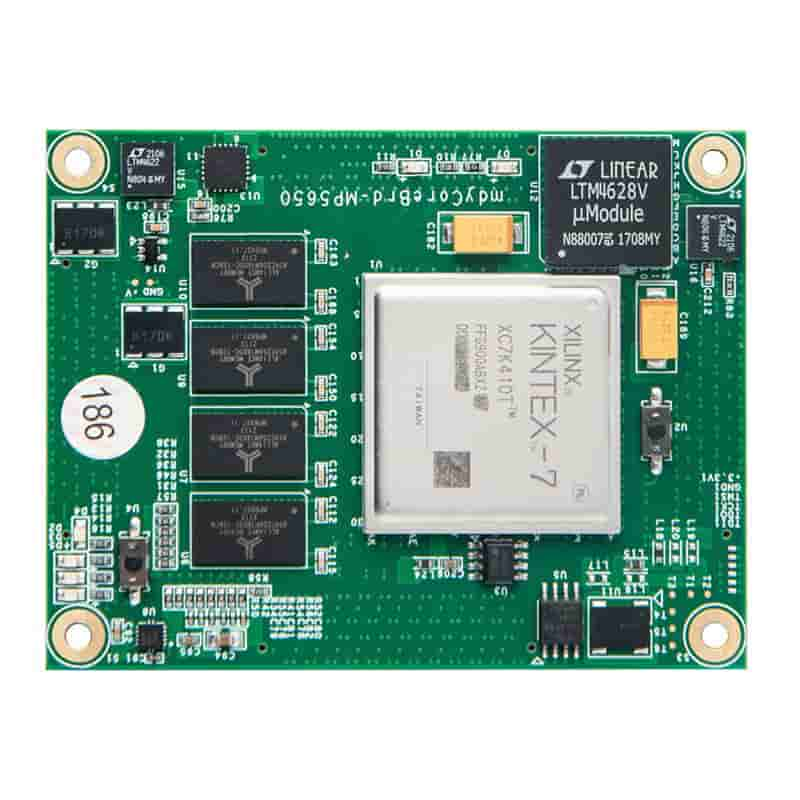

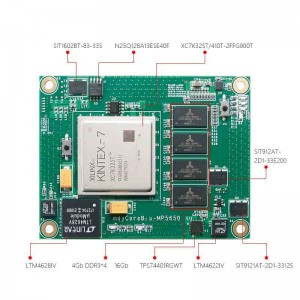

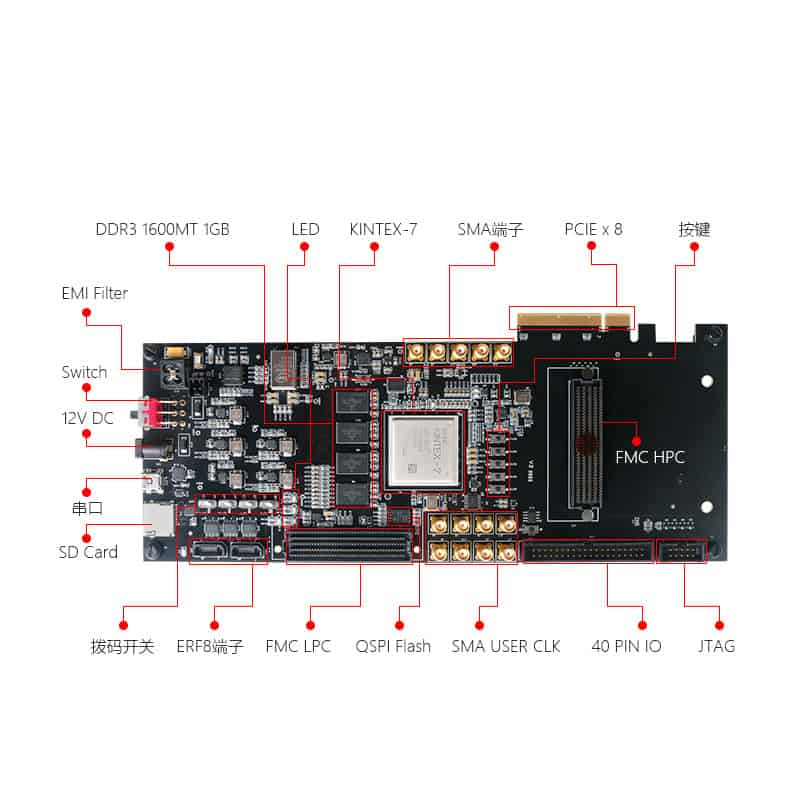

FPGA Xilinx-K7 Kintex7 Xc7k325 410t Gradus Industrialis

DDR3 SDRAMQ: 16GB DDR3, 4GB per unum, 16-bit Data Bit Data Bid SPI Flash: Una pars 128MBITQSPIFLASH, quae ad fasciculos configurationis FPGA et conservationem datorum usoris adhiberi potest. Gradus interfaciei FPGA Bank: adaptabiles 1.8V, 2.5V, 3.3V electrici. Si gradum mutare necesse est, tantum locum correspondentem globuli magnetici mutare debes ad adaptationem efficiendam. Fons potentiae tabulae centralis: EEPROM fons potentiae 5V-12V; M24C02-WMN6TP in instrumento bus I2C fundatur. Modum incipiendi tabulae centralis protocolli secundae lineae sequitur: duos modos incipiendi sustinet, qui sunt connectores JTAG et QSPI Flash. Portus extensus, 120-clavorum, Panasonic AXK5A2137yg MP5700, interfacies SFP laminae inferioris: 2 moduli optici communicationem fibrae opticae celerem, usque ad 6GB/s, consequi possunt. Horologium laminae inferioris: 1 horologium referentiale 200MHz cum tabula principali coniunctum. Pes tubi horologii MRCC, 1 125MHz. Lamina inferior pedum tubi horologii GTX cum tabula principali coniuncta est portus expansionis 40-clavorum: portus extensionis 40-clavorum cum spatio normali 2.54mm reservatur, qui ad modulum designatum ipsius emptoris connectendum adhibetur. Horologium tabulae centralis Essentiae: plures fontes horologii in tabula sunt. Hae includunt horologium systematis 200MHz, horologium GTX 125MHz, et horologium EMCCLK 66MHz. Portus JTAG: 10 suturae, portus JTAG ordinarius 2.54mm, ad demptionem et errores corrigendos. LED programmatum FPGA: 6 lumina LED rubra in tabula principali, quae fontem potentiae tabulae indicant, 4 lumina indicantia signum et pedes tubi FPGA IO directe connexi. Claves: 4 claves. 4 claves. Hae sunt claves FPGA reset, claves Program_b et duae claves usoris.

A: PCB: Quantitas, fasciculus Gerber et requisita technica (materia, tractatio superficiei, crassitudo aeris, crassitudo tabulae,...).

PCBA: Notitiae de PCB, BOM (Documenta probationum...).

A: Fasciculus Gerberianus: CAM350 RS274X

Fasciculus PCB: Protel 99SE, P-CAD 2001 PCB

Index rerum: Excel (PDF, Word, txt).

A: Tua documenta in plena securitate et tuto custodiuntur. Proprietatem intellectualem clientium nostrorum per totum processum protegimus. Omnia documenta a clientibus numquam cum tertiis partibus communicantur.

A: Nulla est quantitatis minimae pretii (MOQ). Productionem tam parvam quam magnam cum flexibilitate tractare possumus.

A: Sumptus vecturae a destinatione, pondere, magnitudine sarcinae mercium determinantur. Quaeso nos certiores fac si pretium vecturae tibi a nobis indicandum est.

A: Ita, fontem componentium praebere possumus, et componentes a cliente etiam accipimus.

Categoriae productorum

-

Telephonum

-

Epistula electronica

-

Whatsapp

-

Skype

-

Skype

-

Skype